|

||||||

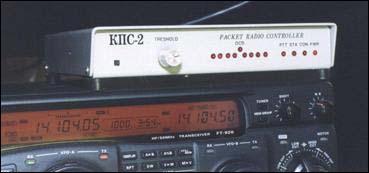

Краснодарский контроллер КПС-2.

Привет

всем, кто заинтересовался. Публикуем

документацию на Краснодарский

контроллер КПС-2. Он

выпускался с 1991 по 1995 год. Сдержит

две прошивки пзу для хоста TF27b и

абонентскуюTiny-2. Демодулятор на петле

ФАПЧ, а модулятор на ЦАП без обрыва фазы.

При разработке

использовались идеи MFJ-1270 и Львовского

варианта. Комплект

документов содержит GIF файлы схем,

расположения деталей, позитивы

печатных плат и прошивки ПЗУ.

Привет

всем, кто заинтересовался. Публикуем

документацию на Краснодарский

контроллер КПС-2. Он

выпускался с 1991 по 1995 год. Сдержит

две прошивки пзу для хоста TF27b и

абонентскуюTiny-2. Демодулятор на петле

ФАПЧ, а модулятор на ЦАП без обрыва фазы.

При разработке

использовались идеи MFJ-1270 и Львовского

варианта. Комплект

документов содержит GIF файлы схем,

расположения деталей, позитивы

печатных плат и прошивки ПЗУ.

![]() kps2a.gif и

kps2a.gif и ![]() kps2b.gif - схема

аналоговой части контроллера, дается

для упрощения понимания ее работы, на

ней также приведены режимы для

настройки её в режиме терминальной

программы .

kps2b.gif - схема

аналоговой части контроллера, дается

для упрощения понимания ее работы, на

ней также приведены режимы для

настройки её в режиме терминальной

программы .

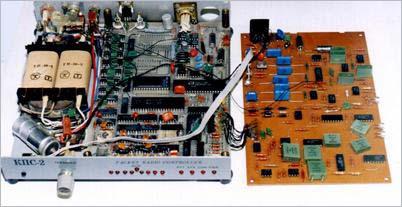

Описание цифровой части контроллера пакетной радиосвязи КПС-2

Цифровая часть контроллера состоит из:

- микропроцессорного блока

- схемы формирования тонов на передачу

- схемы кодирования и декодирования кода NRZI

- схемы тайм-аута на передачу

- схемы сопряжения с RS-232 портом (COM портом компьютера)

- схемы светодиодного индикатора настойки частоты приемника для SSB

- схемы преобразователя -9В и стабилизаторов +5В и -5В

Микропроцессорный блок состоит из:

- микропроцессора Z80 CPU (микросхема DD15)

- постоянного запоминающего устройства (ПЗУ) объемом 32 Кбайта на 4-х микросхемах типа 2764 DD20-DD23 и дешифратором К555ИД4 DD18 для выборки одной из них (возможно использование вместо микросхем 2764 всего одной микросхемы 27256, установленной на месте DD20, при этом выводы 3 и 13 у DD18 необходимо заземлить и 27 вывод микросхемы DD20 соединить с выводом 3 микросхемы DD16)

- оперативного запоминающего устройства (ОЗУ) 32Кбайта на 8-ми микросхемах K565РУ5Д1(2) с мультиплексором адресов на микросхемах К555КП11(14) DD28, DD29

- последовательного асинхронного порта ввода-вывода RS-232 для связи с компьютером и последовательного асинхронного порта ввода-вывода HDLC для связи с трансивером. Оба порта организованы на микросхеме Z80

SIO/0 (микросхема DD27)

- кварцевого задающего генератора на частоту 7372,8 кГц или 14745,6 кГц на микросхеме К555ЛА3 DD3 . На микросхемах DD4 К155ИЕ4 и DD9 К1533ЛЕ1 собран формирователь тактовой частоты 2457,6 кГц со скважностью 2 для процессора. Переключатель на входе микросхемы DD4 при частоте кварца равной 7372,8 кГц должен замыкать вывод 1 с выводом 14, а при частоте 14745,6 кГц - вывод 1 с выводом 12. На микросхемах DD6 К561ИЕ16, DD8 К555ТВ6 и DD10 К176КТ1 cобран делитель частоты для получения тактовых частот последовательных портов RS232 и

HDLC.

Схема формирования тонов на передачу состоит из:

- предварительного делителя частоты на 8 на микросхеме DD5 К155ИЕ5,

- делителя с переменным коэффициеном деления на 16 (тон 1800 Гц = логический 0) или 18 (тон 1600 Гц = логическая 1) для скорости 300 бит в сек и 24 (тон 1200 Гц = логический 0) или 13 (тон 2215 Гц = логическая 1) для скорости 1200 бит в секунду, собранного на микросхемах DD1 К555ТВ6, DD2 К176ЛА7, DD7 К176ЛЕ5, DD11 К561ИЕ11. Скорость 300 или 1200 бит в секунду меняется напряжением на входе 15

"SSB" от соотвествующего переключателя на задней стенке контроллера

"HF/VHF". Такая схема позволяет генерировать тоны с точностью 10 в минус шестой степени с отличной термостабильностью и без разрыва фазы в момент перехода с одного логического уровня на другой

- формирователя синусоидального напряжения с частотой в 32 раза ниже тактовой, состоящего из делителя на 32 на микросхеме DD12 К176ИЕ2, резистивного формирователя ступенчатого напряжения, аппроксимирующего одну четверть периода синуса на резисторах R10-R20, мультиплексора на DD15 К561КП2, подключающего к выходу один из восьми резисторов формирователя, инвертора порядка подключения резисторов на DD14 К176ЛП2, формирующего вторую четверть синуса, и инвертора полуволны синуса на транзисторах VT1, VT2. Синусоидальное напряжение далее через фильтр нижних частот подается на микрофонный вход трансивера.

Cхема кодирования в код NRZI (Non Return to Zero

Inverse) cобрана на инверторе DD2 К561ЛН2 и триггере DD1 К555ТВ6 и служит для уменьшения постоянной составляющей с выходном спектре сигнала. Декодирующая схема собрана на микросхеме ПЗУ К573РФ2 DD19, в которой записана таблица переходов декодирующего конечного автомата

(State Mashine) и микросхем параллельных регистров DD24, DD25, К561ИР9, где сохраняются промежуточные состояния этого автомата.

Схема прерывания (Time-Out) сигнала на передачу при "зависании" процессора собрана на одновибраторе со временем срабатывания 40 сек. (DD26 К561ЛН2)

Cхема сопряжения с портом RS232 компьютера состоит из инвертотов с гистерезисом DD38 К155ТЛ3 и преобразователях уровня в =/- 12В на операционных усилителях К140УД7 DA1, DA2, DA3.

Схема индикатора настройки, необходимая при работе в

SSB, собрана на транзисторных (VT4-VT8, VT10-VT14) компараторах с линейным нарастанием порогов их врабатывания. На них подается сигнал с выхода ФАПЧ днмодулятора (см. аналоговую часть). При точной пастройке светодиоды будут гореть симметрично, относительно середины индикатора. .

Схема источника минусового напряжения состоит из генератора на таймере К1006ВИ1 (DD39) и инвертора на DD40 , выходы которых выпрямляются диодным мостом и стабилизируется на уровне -5В транзистором VT14 и операционным усилителем DA5 К140УД7. Стабилизатор +5В собран на DA4 К142ЕН5В с защитой от перенапряжения по входу VD7 Д815Ж и выходу VD21 Д815А

Авторы.

Разработчик цифровой части – В.А. Кияшко (RZ6AT),

RZ6AT@RW6AT.KRD.RUS.EU, bobkey@mailru.com ,

Разработчик аналоговой части - М.А. Салмин (RW6AT),

RW6AT@RW6AT.KRD.RUS.EU, msalmin@chat.ru .

Возьмите полный комплект документации: